|

价格:29900元

(包含中国大陆,港澳运费,

及组合遥控器一个。

组合遥控器可控制本机及睿志大部分最新款

前级耳放。遥控器需用户自备两个AAA电池。)

购买有机玻璃顶板价格:200元。

俩外壳版本可选,下单时务必说明否则随机发货:

R-7HE MK3黑色

R-7HE MK3银色

2025年5月15日始顶板增加散热孔,即便旧的版本没有散热孔,产品也能安全长期开机完全不影响使用寿命:

点击下载USB驱动

Amanero

combo 384

R-7HE MK3与R-7HE MK2 差别:

两者差别是机箱与显示屏,其他部分是一样的。

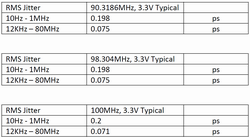

独一无二的Jitter消除技术:

Jitter 一直被认为是数码系统声音实际表现不如高档模拟系统的根源。

传统的一些DAC设计,对于时钟的处理方法是跟随捕捉以还原信号源的时钟,有些还有修正缩小Jitter的功能

,但如果信号源的Jitter较大,效果就有限。

对于设备测试时这种方案更容易获取高分,但当实际使用中,多数的信号源都具有较大的Jitter

,以致音质表现不如人意。

有些只需花1000元就可以买到的DAC,指标上比销量不俗的某

些外国品牌数万元DAC还要好。有谁会认为这1000元的DAC是更好听

?这就象是不久前国内某机构直接拿两个品牌的汽车对撞后网友形容在测试中得高分的车:“测试没输过,实战没胜过。”

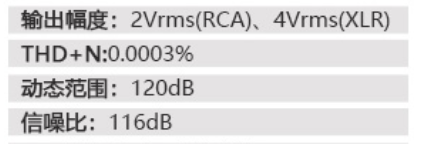

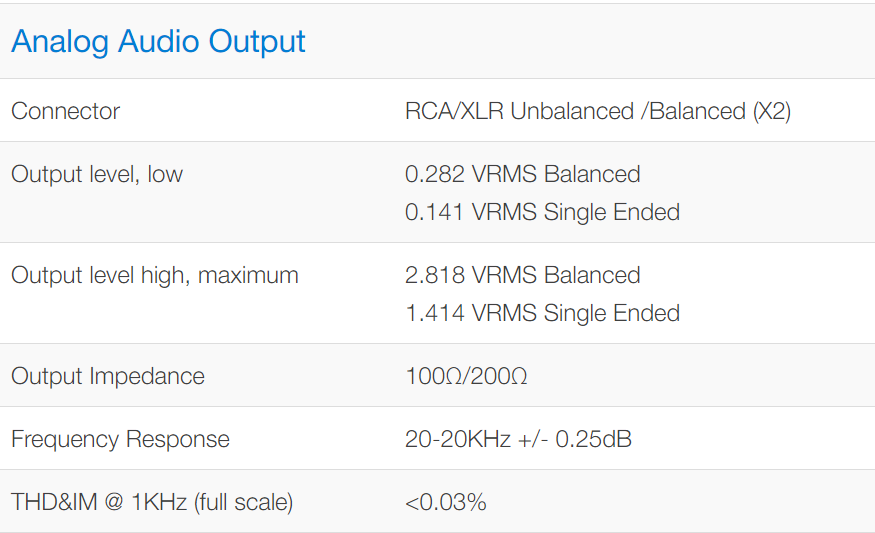

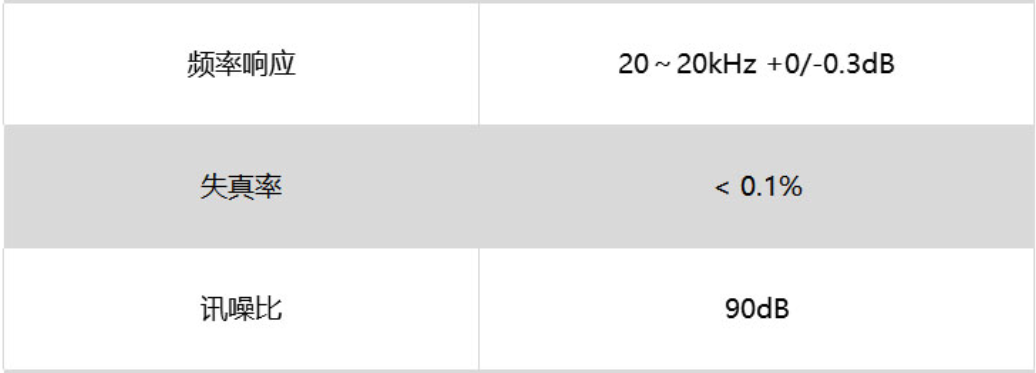

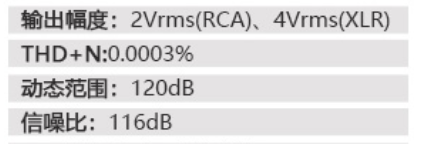

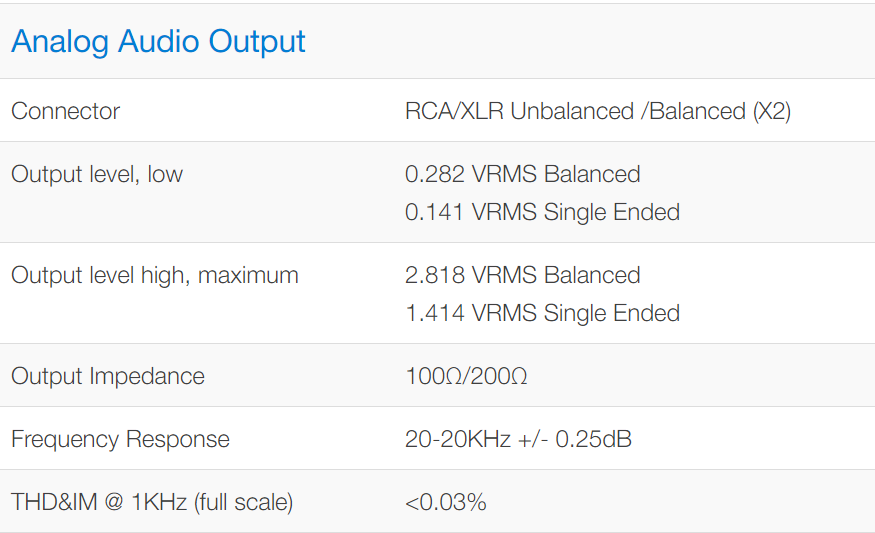

以下三个产品图表来自三个不同其他品牌,猜哪个最便宜?(答案在本页最底部)

产品A

产品B

产品C

为了完全杜绝信号源Jitter的影响,在本机中,采用的是异步的时钟方式去处理。

先读取并储存一定数量的信号源数据到

机器的RAM中,舍弃使用信号源的时钟,而直接使用本机的高性能Accusilicon时钟与RAM中的数据进行同步输出。由于数据与时钟均是内部传输,可忽略传输对Jitter的影响,Jitter

值就是本机所用的时钟参数。

这种处理方式的关键在于保证数据传输完整性,这就是技术上的秘密。

在传输数百万个数据中只要丢失了任意一个数据,都可以在聆听音乐时出现一个尖锐,明显,象黑胶碟系统中静电的“啪” 声。

何先生对音乐热爱,总能在聆听音乐时激发出各种新构思,而我们不仅自己拥有软硬件技术优势,更对音乐有着正确理解,无需依赖外聘人员,即时可以直接实践聆听中突发的构思,追求并实现最逼真的声音还原。

由于本机时钟与信号源时钟的完全隔离独自运行,传统的测试方法已不能测试本机Jitter

的性能,需要特制的数据采集电路测试。对于普通用户来说,最佳的测试方法就是聆听,几无Jitter 的声音非常逼真自然,清澈如水

,模拟味十足。

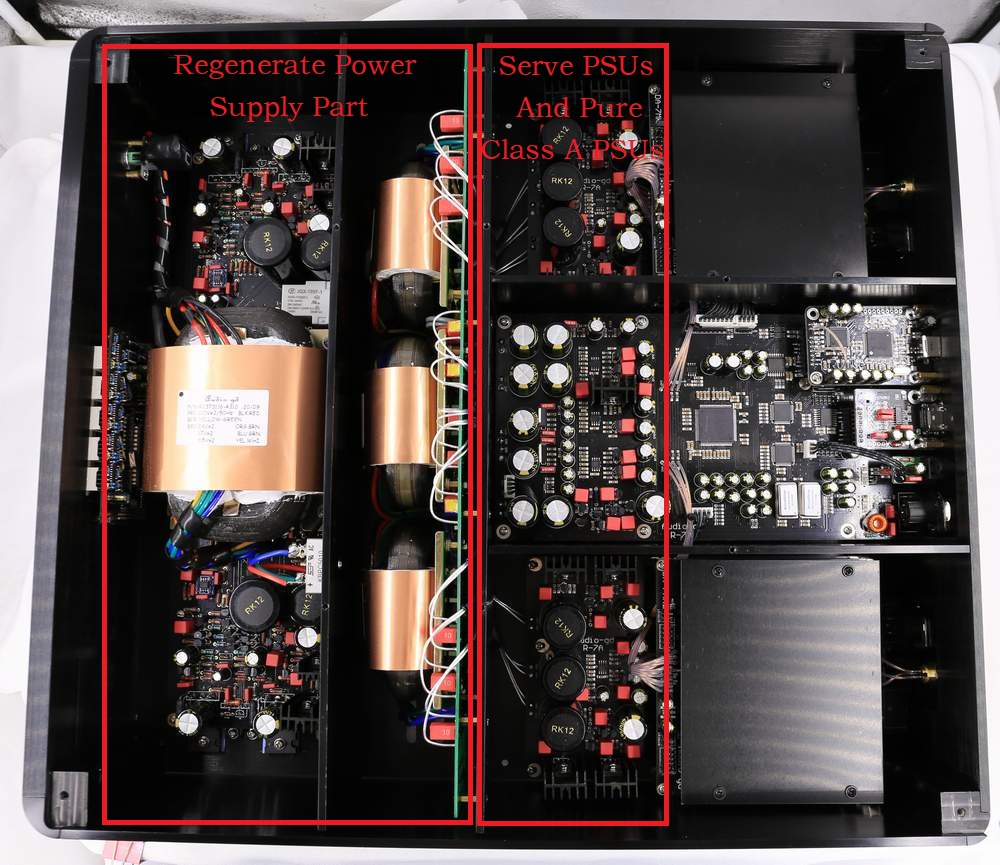

R-7HE MK3 的特性:

1, 全分立件真正平衡电流传输设计。

4组全分立件单独的 DSD 硬件解码器。

8组全分立件R-2R DA模组组成两声道平衡推挽解码器。

运用最新设计的分立伺服稳压电源专门供电到数码电路,性能可媲美电池但又避免了电池供电声音干瘦的特性,且令本产品工作温度远低于旧有型号。时钟电路与模拟电路依然使用最佳声音搭配的纯A类稳压电源供电。(新升级)

2,

通过长时间聆听黑胶唱机系统,我们成功将模拟黑胶声音特性做到本产品中,通过按键去控制是否加入模拟功能。(新升级)

3, USB与HDMI输入均分别配备隔离器,及两组线性电源分别对隔离器前的USB 与HDMI

分离供电 ,杜绝信号源的干扰。

a, USB使用双向传输隔离器,既向FPGA处理器传输IIS信号,也接收FPGA处理器发送的

同步时钟信号,USB界面本身不再装备数据时钟,

使用同步时钟令信号传输更精准,令音质大幅度提升到优于上代R-7HE

加DI-20 (但不是DI-20HE)的音质效果。

b, HDMI配备独立隔离器提升了HDMI输入的音质。

4, 显示输入信号采样率功能。

5, 10MHz时钟输入接口,可以连接外部的时钟发生器

(默认50欧,可定制75欧)。

6,

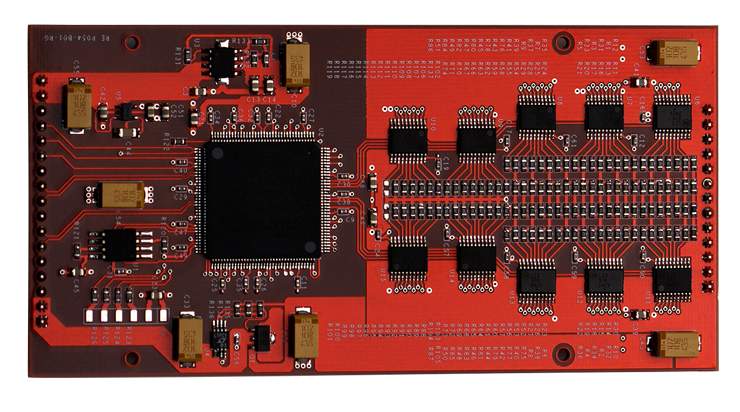

整机数字电路全部由1片FPGA 与 7片CPLD可编程器件组成 ,使不同功能电路分离以隔绝干扰,应用传输速度最快的并行数据处理模式,且支持升级固件以提升音质效果。

FPGA数据处理模式为并行处理模式。

IIS信号是串行数据模式,每个数据都需要一个时钟周期,一帧左右声道数据需要64个时钟周期

,受到64个时钟周期稳定性的影响。

而并行模式只需要一个时钟就可以传输及处理左右声道的32位数据,大大提高了运行处理速度且更不受时钟稳定性的影响。

IIS输入数据(USB与HDMI-IIS)

一输入就立即被重组成两组32位并行数据。SPDIF信号解调后也通过两组24位并行数据方式送到下一级处理。DSD数据也是一输入就重组成

两组64位并行数据处理。

经对比聆听,并行处理模式可以令声音更清晰中性,动态更佳而更具模拟味。

7,

两个频率高达90 / 98MHz Accusilicon 时钟提供整机同步时钟,无需经过PLL升频即可应用于高码率音乐播放。

新构架的时钟管理设计,时钟工作更稳定

,透明度更高细节更丰富。

8, DSD使用内置异步时钟重新校对,明显提高播放的清晰度与动态。

9, SPDIF 支持DOP播放。

10,

所有数字模式设置均可在面板上完成 (无需打开机器)。

11,

机器后板安装有固件升级接口(升级固件无需打开机器)。

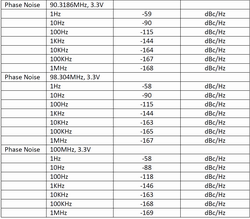

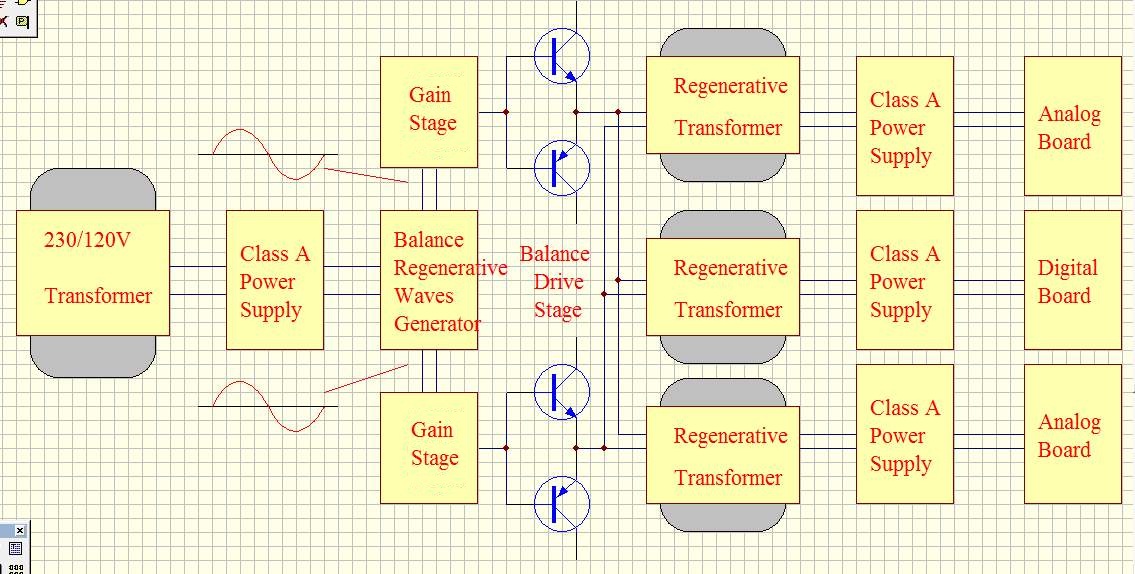

全模拟再生电源技术:

再生电源供电就象是在机器内置了一台私人专用的发电机。

它可以最大限度地滤除电源线上干扰,提供超级纯净的电源

供电到音频放大器,

还原出极低音染又极具模拟味的信号给音响系统及用户。

再生电源的设计中,120V / 220V的交流电源经过再生电源输入变压器,转换到直流电源,再经过甲类并联稳压电源供电到再生波形发生器及驱动器。

一组平衡的再生标准波形发生器产生出超低失真的50Hz波形,经过平衡的增益放大器及强大的

驱动级,以驱动三个再生电源输出变压器输出纯净而电压及频率稳定的电源,再由十三组甲类并联稳压电源对左右声道的

模拟音频放大器及不同处理功能的数字音频部分进行独立供电。

再生波形发生器及驱动器均经过甲类稳压电源供电,令其工作不受市电变化及干扰所影响。

甲类并联稳压器具有极高的输入阻抗以阻隔干扰,避免通过市电电源的干扰进入音频电路影响了音质,同时也避免了左右声音信号通过电源产生的串音以提高分离度。而输出阻抗低则具有极佳线性与速度,是极为优秀的电源稳压电路设计。

Audio-gd

在再生电源设计上的论点:

1,

通过对 AP SYS-2722的内部设计分析及实际测试对比,

纯模拟的再生标准波形发生器的失真比数字合成发生器低很多。

2, 数字驱动级可以有更高的电源转换效率,但完全模拟的驱动级则有更多的模拟味。

3, 400Hz再生波形频率有更高电源转换效率,50Hz再生波形频率比400Hz更远离人的听觉灵敏区,音质更醇厚自然。

我们经多番对比后决定采用50Hz的频率。

R-2R DAC 的优缺点:

优点 :

1, R-2R

不会将时钟信号转换到输出信号。

2, R-2R 不敏感于 jitter 但

Delta-Sigma 就相当敏感。

3,

R-2R的输出信号电平的精准度高于Delta-Sigma .

缺点 :

1, R2R

的谐波失真度可以做到相当低但还不能做到象ES9038

PRO (Delta-Sigma)那样的低谐波失真。

2, Glitch

与梯阶电阻的精度不容易解决。

市场上流行的R-2R设计:

无论是DIY套件或是厂制品,R-2R已经变得流行。

在低价位的DIY 套件市场,通常的设计是学习了MSB旧有技术,但仅保留了信号转换的部分而舍弃了原厂精妙的设计。这种设计是通过数据串行输入到移位寄存器IC去将数据

转换到模拟信号的转换,是根本无法解决R-2R的技术难题,这种设计的性能是完全依赖梯阶电阻的精度。

在Hi -End

市场的厂制品,使用了相当复杂的技术去解决R-2R存在的问题,从而达到高性能与音质。

一些厂家使用移位寄存器IC的串行控制模式。下图的设计是使用了FPGA并行控制梯阶电阻开关的方式。并行控制模式,每一bit的梯阶电阻开关都单独控制,因此具有超高速度

(并行模式仅需1个时钟周期去输出所有数据, 串行模式则需要至少8到24个时钟周期)去发送或更新数据,并可以在任何时候即时纠正数据从而令输出信号具有低失真特性,解决由于电阻公差及Glitch等引致的问题。

梯阶电阻的精度:

很多人只关心梯阶电阻的精度,

他们看来R-2R就是取决于电阻的精度。

现今,24

bit已是一个标准,但可制造的电阻精度是否可以达到24 bit?

即使是16 bit,

精度要求已是1/66536, 即使是 0.1% (1/1000)的电阻精度,是完全不足够的。就算是0.01%

(1/10000),也依然未能达到 16 bit的要求,更不要说是24 bit.

因此电阻的精度并不是解决问题的方向。假如世界上有0.00001%的电阻,能达到24

bit的要求,但梯阶电阻的开关内阻的离散性,会将这个超级高精准度

的优势完全抹去。

我们要从技术上解决问题,而不是单凭提高电阻的精度。但我们依然在产品中使用超高精度的电阻。

相当重要的FPGA/CPLD:

FPGA/CPLD是可编程的逻辑阵列器件。

现今,FPGA已应用在不少 Hi-End级别的DAC产品中,

象流行的ROCKNA WAVEDREAM DAC.

自2008年我们开始在DAC产品中使用FPGA设计。

本机由1片FPGA,7片CPLD

芯片组成整机数字电路。

FPGA内部的硬件布局,可以通过软件去设计与排布,并且硬件是可以通过软件

更新进行升级。

当升级固件时,硬件就会同时得到升级。这样的设计具有相当高的灵活性,可以通过软件升级实现音质的提升,增加更多更新的功能,以及令产品永远不会落后于时代。

责任重大的FPGA/CPLD:

1,FPGA 内建高性能SPDIF解调器,而不采用市场上固化低性能的SPDIF解调芯片如

DIR9001, WM8805 and AK411X 等.

2,重组时钟及FIFO技术,输出数据可以精准同步到时钟上,拒绝jitter.

3,内建 2X, 4X

and 8X 数字滤波器,及不同算法NOS模式可供用户选择最贴合个人口味的音色。

4,通过独特设计模拟黑胶碟播放系统的音色。

全分立件输出级:

信号经过最后一级是模拟输出级,输出级对DAC的音质影响是决定性的。再优秀的数字电路设计,没有一个优秀的模拟输出级设计,音质也会变得极其普通。

模拟输出级使用高速的CAST放大器担任信号的放大与处理,CAST放大器是没有负反馈的设计,且工作于电流信号模式,而不必象其他的设计一样,将信号反复在电流与电压间多次变换。CAST只需要一级的电路就可以完成信号的处理,而其他传统电路或OPA设计,则有2-6级的电路去处理信号,CAST处理方式具备了最小的音染。

输出级是工作于纯A类的状态,完全没有负反馈,

且具备强大输出驱动力,可以缩小信号线对音质的影响,重现纯净与逼真的声音信号。

DAC内建四个OPA运放担任直流伺服功能,这样DAC就无需耦合电容也可以正常工作,避免了电容产生的音染。

在DA

模块后的所有信号通道,没有使用任何开关元件以实现最真最纯的音质效果。

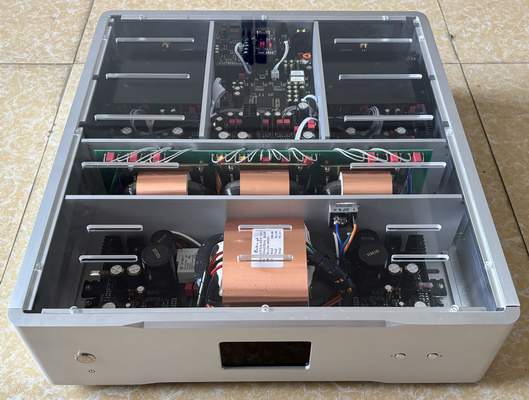

强大的电源设计:

使用4个总功率达 295 W 高性能R牛及超过7万UF的音频滤波电容保证供电的纯净度

。

10组全新设计的分立伺服稳压电源,7组超高速线性稳压电源对本产品数码电路进行分离供电。

7组分立件的甲类并联稳压电源分别对再生电源驱动器及模拟音频各部分分离进行供电。

全部电源都具有超高速及超低噪音的特性。

布局

:

DAC使用5MM厚的铝板去分隔开数字部分,左与右声道模拟部分及变压器部分,以避免它们之间的相互干扰。

即使是电源输入插座,内部的AC电源线,都使用铜盒铜槽进行屏蔽以避免干扰到信号线路。

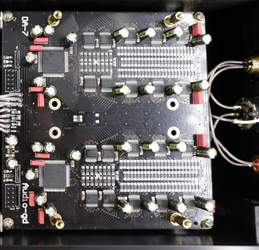

左右声道的模拟部分使用对称布局分布于数字部分两侧,具有相同的信号线长度与距离,令音质更精准。

DA 7 模块安装到两块铝板中间以避免其他电路的干扰。

繁复的布局与安装工艺只因为了音质更清晰纯真,背景更宁静,音场更宽广。

产品A:USD150 DAC

产品B: USD5000+ 美国P品牌DAC

产品C:USD10000 英国E品牌RIAA前置

|