|

价格:(包含中国大陆,港澳运费)

全时钟升级版 : 5799元

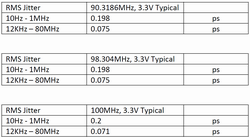

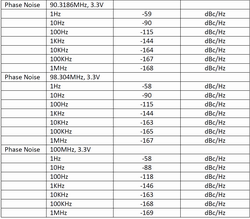

主板使用的Accusilicon clocks:

点击下载USB驱动

Amanero

combo 384

R-1 (2021款)的特性:

1, USB既向FPGA处理器传输IIS信号,也接收FPGA处理器发送的同步时钟信号,USB界面本身不再装备数据时钟,

使用同步时钟令信号传输更精准,令音质大幅度提升到接近上代R-1

加DI-20 (但不是DI-20HE)的音质效果。(新升级)

3, FPGA数据处理模式为并行处理模式。

IIS信号是串行数据模式,每个数据都需要一个时钟周期,一帧左右声道数据需要64个时钟周期

,受到64个时钟周期稳定性的影响。

而并行模式只需要一个时钟就可以传输及处理左右声道的32位数据,大大提高了运行处理速度且更不受时钟稳定性的影响。

IIS输入数据(USB与HDMI-IIS)

一输入就立即被重组成两组32位并行数据。SPDIF信号解调后也通过两组24位并行数据方式送到下一级处理。DSD数据也是一输入就重组成

两组64位并行数据处理。

经对比聆听,并行处理模式可以令声音更清晰中性,动态更佳而更具模拟味。

4, 新构架的时钟管理设计,时钟工作更稳定

,透明度更高细节更丰富。

5, DSD使用内置异步时钟重新校对,明显提高播放的清晰度与动态。

6, SPDIF 支持DOP播放。

R-2R DAC 的优缺点:

优点 :

1, R-2R

不会将时钟信号转换到输出信号。

2, R-2R 不敏感于 jitter 但

Delta-Sigma 就相当敏感。

3,

R-2R的输出信号电平的精准度高于Delta-Sigma .

缺点 :

1, R2R

的谐波失真度可以做到相当低但还不能做到象ES9038

PRO (Delta-Sigma)那样的低谐波失真。

2, Glitch

与梯阶电阻的精度不容易解决。

市场上流行的R-2R设计:

无论是DIY套件或是厂制品,R-2R已经变得流行。

在低价位的DIY 套件市场,通常的设计是学习了MSB旧有技术,但仅保留了信号转换的部分而舍弃了原厂精妙的设计。这种设计是通过数据串行输入到移位寄存器IC去将数据

转换到模拟信号的转换,是根本无法解决R-2R的技术难题,这种设计的性能是完全依赖梯阶电阻的精度。

在Hi -End

市场的厂制品,使用了相当复杂的技术去解决R-2R存在的问题,从而达到高性能与音质。

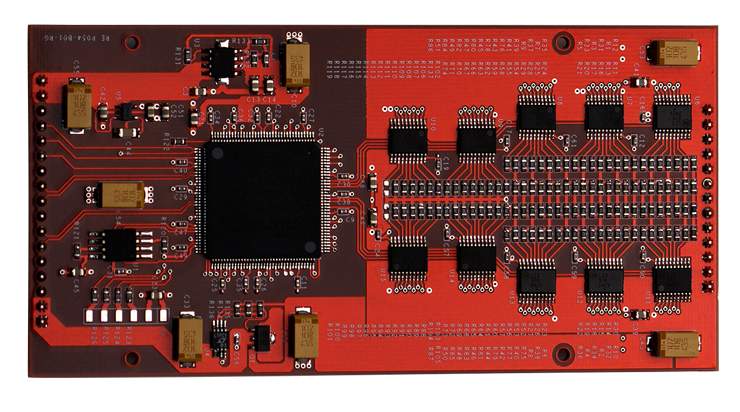

一些厂家使用移位寄存器IC的串行控制模式。下图的设计是使用了FPGA并行控制梯阶电阻开关的方式。并行控制模式,每一bit的梯阶电阻开关都单独控制,因此具有超高速度

(并行模式仅需1个时钟周期去输出所有数据, 串行模式则需要

至少8到24个时钟周期)去发送或更新数据,并可以在任何时候即时纠正数据从而令输出信号具有低失真特性,解决由于电阻公差及Glitch等引致的问题。

梯阶电阻的精度:

很多人只关心梯阶电阻的精度,

他们看来R-2R就是取决于电阻的精度。

现今,24

bit已是一个标准,但可制造的电阻精度是否可以达到24 bit?

即使是16 bit,

精度要求已是1/66536, 即使是 0.1% (1/1000)的电阻精度,是完全不足够的。就算是0.01%

(1/10000),也依然未能达到 16 bit的要求,更不要说是24 bit.

因此电阻的精度并不是解决问题的方向。假如世界上有0.00001%的电阻,能达到24

bit的要求,但梯阶电阻的开关内阻的离散性,会将这个超级高精准度

的优势完全抹去。

我们要从技术上解决问题,而不是单凭提高电阻的精度。但我们依然在产品中使用超高精度的电阻。

相当重要的FPGA:

FPGA是可编程的逻辑阵列器件。

现今,FPGA已应用在不少 Hi-End级别的DAC产品中,

象流行的ROCKNA WAVEDREAM DAC.

FPGA内部的硬件布局,可以通过复杂的软件去设计与排布,并且硬件是可以通过软件的升级而得到升级。

当升级固件时,硬件就会同时得到升级。这样的设计具有相当高的灵活性,可以通过软件升级实现音质的提升,增加更多更新的功能,以及令产品永远不会落后于时代。

相当重要的FPGA/CPLD:

FPGA/CPLD是可编程的逻辑阵列器件。

现今,FPGA已应用在不少 Hi-End级别的DAC产品中,

象流行的ROCKNA WAVEDREAM DAC.

自2008年我们开始在DAC产品中使用FPGA设计。

本机由1片FPGA,5片CPLD

芯片组成整机数字电路。

FPGA内部的硬件布局,可以通过软件去设计与排布,并且硬件是可以通过软件

更新进行升级。

当升级固件时,硬件就会同时得到升级。这样的设计具有相当高的灵活性,可以通过软件升级实现音质的提升,增加更多更新的功能,以及令产品永远不会落后于时代。

责任重大的FPGA/CPLD:

1,FPGA 内建高性能SPDIF解调器,而不采用市场上固化低性能的SPDIF解调芯片如

DIR9001, WM8805 and AK411X 等.

2,重组时钟及FIFO技术,输出数据可以精准同步到时钟上,拒绝jitter.

3,内建 2X, 4X

and 8X 数字滤波器,及不同算法NOS模式可供用户选择最贴合个人口味的音色。

4,通过独特设计模拟TDA1541+SAA7220的音色。

强大的电源设计:

DAC 内建13组超高速超低噪音电源

并组成双重稳压以更好消除电源噪音,供电到各不同部分。

|