|

Price: (

Exclude shipping cost .Please send your address, name to

audio-gd@vip.163.com

get the quote.

)

R-28 MK3 (Accsilicon clock

version): USD1299

Black and silver two chassis versions available,

customer must inform while place the order ,otherwise we ship the

edition randomly:

Include combo remote controller.

It need two AAA batteries support by users .

Purchase the metal remote controller

simultaneous price is USD40

If want to connect the USB to

Windows ,Click to download the

driver of

Amanero

combo 384

The different

between R-28 MK3 and all previous generation:

Apply the isolator to separate the digital

and analog parts , improved on the whole unit design , made the

sound quality with obvious upgrade.

R-28 MK3 feature:

1, Built in isolator for total isolate

of the digital and analog parts .

2, Fully balance discrete transistors

headamp / preampamps and DAC all in one model, the headamp max

output power achieve 9500 mW ,no matter to drive most headphones .

3, The unit has two gain modes, the 12DB on low gain for drive

the headphone which has over 95DB sensitivity, and 22DB on high

gain cooperate with the strong power ability, enough to drive the HE6 which has around 85DB

sensitivity headphones.If customer want to boost 6-12DB gain, in

total 28-34DB gain.

4, Dual transformers

power supply separately, built in 10 ground ultra speed linear PSUs

and two ground pure class A PSUs

5, Real balance DAC design ,built in 4 group

fully discrete real balanced DSD native decoders , 8 group fully

discrete R-2R PCM decoders and 32bit / PCM384K /DSD512 asynchronous

transfer Amanero 384 .

6, USB transmit the IIS signal to the FPGA processor and receive the

clock signal from the FPGA processor, the USB interface without on

board data clocks, the signal transmit is much exact, the sound

quality get the much improve .

7, The FPGA process data in the parallel mode.

The IIS data is series transmit

mode, every data must need one clock cycle to process or transmit,

one frame data ( Include L and R data) must need 64 clock cycle to

process or transmit, so the data has effect by the 64 clock cycles.

But the parallel data process

and transmit mode only need one clock cycle can finish the one frame

data process

and transmit, that can avoid the effect of clock stability .

The IIS input (Include USB and HDMI-IIS) has recombine become dual

32bit parallel data once input , and the SPDIF input after decoder, has

recombine become dual 24bit parallel data, and the DSD input has

recombine become dual 64bit parallel data once input.

The parallel process and

transmit mode can improve the sound quality on the transparency and

detail but still analog.

8, Full new configuration clock

manage design built

in, improved on the clock timing.

9, DSD asynchronous clock technology

has apply that improves the sound quality obviously.

10, DOP support from SPDIF input .

Pros and cons of R-2R DAC :

Advantages:

1.R-2R will not convert the clock signal into the output

signal.

2. R-2R is not sensitive to jitter .Delta-Sigma D/A is much

more sensitive to jitter.

3. The output signal is much more precise compared to

Delta-Sigma D/A .

Weaknesses:

1.THD today is extremely good with Sigma Delta chips in

comparison to R2R ladders are good too but not as good.

2. Glitches and accuracy of the ladder resistors are very

difficult to avoid and require complex technology to resolve it.

R-2R basic design in the market:

The

R-2R DAC is very popular nowadays and available from DIY kits up to

completely high-end products.

In the low range DIY market, the R-2R design is often

based on old technology designed a long time ago by MSB and only

includes basic R2R ladder design and do not include the wonderful

correction design of the original MSB technology. This design uses

data shift registers logic chips in series mode to convert the data

to an analog signal. The structural R2R technology issues cannot be

avoided, and performance is solely depending on the accuracy of the

ladder resistors.

In the High-End market the R2R design is much more complex and

achieves better performance. A basic R2R ladder is simply not

sufficient enough to achieve good performance and high sound

quality! Some manufacturers are using shift registers design. A less

complex and less efficient design based on traditional logic chips

working in serial mode to correct the ladder.

A far better design switches resistors in parallel mode. An

ultra-fast FPGA controls and corrects the R2R ladder. The parallel

design mode controls every bit respectively and therefore achieve

unprecedented performance. (In parallel mode only 1 clock cycle is

needed to output all data; serial design mode needs at minimum 8 up

to 24 clock cycles) The parallel design is much more complicated.

Once designed properly it can correct every bit of the ladder.

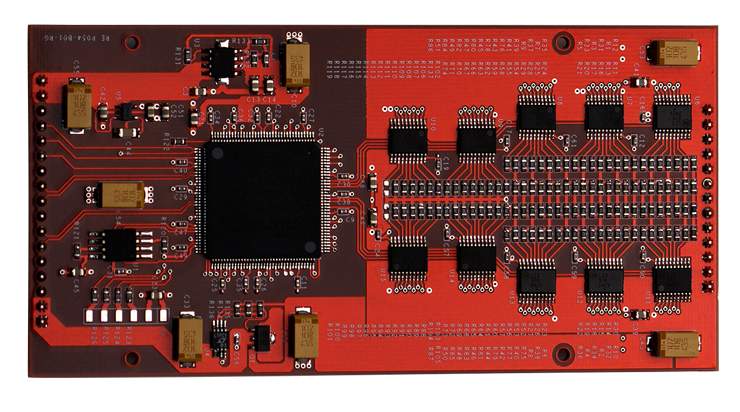

Photo below shows a design with such FPGA, can correct the

unavoidable imperfections of the R2R ladder caused by intolerance of

resistors glitches and achieve best performance.

Accuracy of the ladder resistors (tolerance):

Many

people believe the tolerance of the resistors in the ladder is most

important to reach best performance. Nowadays 24 bit resolution is

standard. What tolerance is needed to achieve 24 bit resolution?

When we look at 16 bit the tolerance of 1/66536, 0.1%

(1/1000) is far not enough, even a tolerance of 0.01% (1/10000), the

best tolerance available in the world today, still cannot handle 16

bit correctly; we are not even calculating 24 bit here!

The tolerance of the resistor will never solve

Imperfections of a ladder. This would require resistors with a

tolerance of 0.00001% and ability to handle 24 bit resolution. This

is only in theory because the discreteness of the switch logic chips

have already too much internal impedance and will destroy the

impossible tolerance of a the resistor.

The solution is to correct the ladder and not to depend

on the tolerance of resistors. It��s a combination of both: Ultra-low

tolerance resistors controlled by a correction technology and very

high speed FPGA which is applied in in our design.

Importunacy of the FPGA/CPLD:

FPGA

stands for Programmable Array Logic.

Nowadays the FPGA is applied in a lot high end grade

DACs; like the popular ROCKNA WAVEDREAM DAC.

We have

applied the FPGA in our DAC products since 2008.

R-28 MK3 has built

in 1 pc FPGA and 5 pc CPLD programmable chipsets to separate the different

configured circuits for avoid interrupt.

The internal hardware design is fully controlled by

complex software. A huge advantage is the fact the software in the

FPGA can easily be upgraded offering new features or improve the

performance. Such design is much flexible and future proof!

�@

FPGA/CPLD tasks :

1. The FPGA

high performance SPDIF interface, replacing

traditional SPDIF interface chips like DIR9001, WM8805 or AK411X wich

are lower in performance in comparison to FPGA.

2. Full re-clocking process with FIFO design applicable

on all inputs. This way the output data keeps fully synchronized

with the clock signal to reject any jitter.

3. Built in 2X, 4X and 8X oversampling and digital

filters and on top of this 4 different true NOS (only analog 6dB

filtering) modes. To completely configure it to your liking!

4. Built in the

especial design to simulate the vinyl record sound flavor.

Built in an excellent real balance discrete amp

The

signal last stage is the analog output stages, which have paramount

effect the final DAC sound quality.

After d/a conversion by the R2R D/A modules the analogue

signal is transported by fully discrete matched-transistor output

stages.

The high speed special ACSS output stages are non-feedback

and current driven design.

They are Special because almost all other designs need to

convert the signal multiple times from and to current or voltage,

resulting in less detail and less defined soundstage .

The

output stages have built in 4 pair 15W transistors to offer strong

drive capanility .The diamond differential design can avoid switch

distortion , it is working in a class A but don't draw large

current while idle . The balance drive mode can kill the noise and

distortion and improves the soundstage presentation ,background and

the transparency ,ect.

0.05% tolerance volume control system

There

4 channels volume boards are built in into the unit for a balance

volume are control by digital signal applied relaies control the

resistors in analog area . The 0.1% Vishay or KOA resistors working

in parallel mode to got the 0.05% tolerance . ( I don��t know

technical design so I can��t correct this part)

Heavy power supplies design:

The

DAC has the high quality low noise, low flux leakage, R-cores

transformers to supply all digital parts as well as left and right

analog boards.

There are in total 10 groups ultra-high speed and

ultra-low noise PSUs allowes get very

clean power supply for the digital parts of DAC.

There are two groups of pure class A PSUs built in for

the analog amps .

�@ |