|

Price:

( Exclude shipping cost)

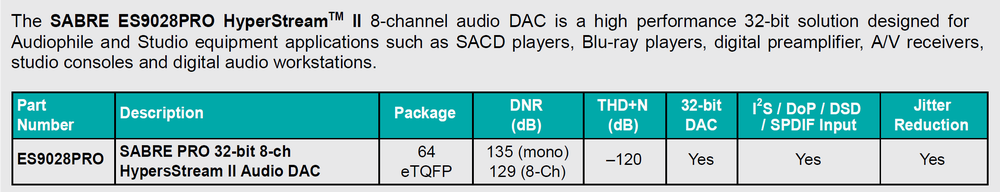

D-57 standard version: USD768

(Dual ES9028Pro, stock clocks)

D-57 Full Clocks upgrade version: USD888

(Dual

ES9028Pro,Femtosecond

Accusilicon *2 )

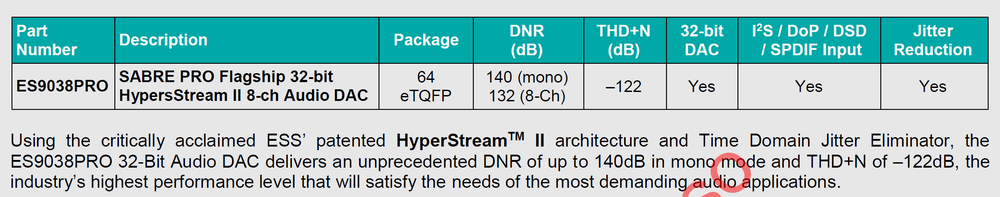

D-77 standard version: USD908

(Dual ES9038Pro, stock clocks)

D-77 Full Clocks upgrade version: USD1033

(Dual

ES9038Pro,Femtosecond

Accusilicon *2 )

Please send your address, name

to audio-gd@vip.163.com

get the quote.

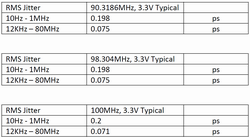

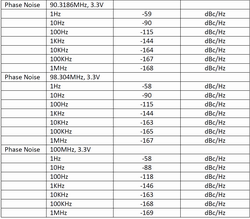

Accusilicon clocks:

Click to download the

driver of

Amanero

combo 384

D-57/77 (2021 version) feature:

1, USB transmit the IIS signal to the FPGA processor and receive the

clock signal from the FPGA processor, the USB interface without on

board data clocks, the signal transmit is much exact, the

sound quality get the much improve , close to the last

generative D-77 combine with DI-20 (But not DI-20HE) level.

2, The ESS9028PRO/9038PRO clock has apply the same

clock of the FPGA.

The different between

dual ES9038 Pro and single ES9038 Pro is large:

The different not only the DNR, but the

dual ES9038 Pro working under mono mode, the channel crossing is

improved for offer a larger and exact sound stage.

Even the

ESS9028 Pro, working under mono mode, its DNR had 3DB better than

one ES9038 Pro .

The FPGA is

important in the D-77:

1,

Separate the data feed to dual ES9038 Pro for working in mono mode.

2, Clock re-clock process and FIFO design for all inputs

, the output data can exact synchronisation with clock signal,

reject jitter.

3, Built in high performance SPDIF interface

, bypassing low performance SPDIF interface

of the ES9038 Pro .

What is the FPGA duty

in the D-77:

1, Separate the data feed to dual ES9038 Pro for working in mono

mode.

2, Clock re-clock process and FIFO design for all inputs

, the output data can exact synchronisation with clock signal,

reject jitter.

3, Built in high performance SPDIF interface

, bypassing low performance SPDIF interface

of the ES9038 Pro .

Full discrete output stages:

The

signal last stage is the analog output stags , they greatly effect

the whole DAC sound

quality.

The output stages working after ES9038 pro, they are full

discrete transistor built with hole parts but not SMD parts

.

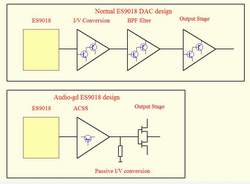

The high speed ACSS amps

work as the signal gain and processing , they are of non feedback

design and working in current signal mode . the dual ES9038 pro

output [current signal] goes through the ACSS amp

.

In our design output stages working in pure class A ,

and without any negative feedback for the most pure and life like

sound reproduction .

There are 4 pcs OPA built

in as DC servo , so the DAC can

be working well without coupling caps and output the most neutral

sound.

Heavy power supplies design:

There are in total 16 groups PSUs .

A total 13 groups of ultra speed linear PSUs

(dual stages PSU to

remove the power interruptions ). PSUs deliver

cleanest power to allow digital circuits working under best

conditions .

2 groups of pure class A PSUs to

power to the analog circuits and deliver most analog sound .

The control and display circuits are powered by a

separate PSU

to avoid adding any additional noise to the rest of the circuit.

|